Digital Circuits and Systems

The focus of the digital circuits and systems group is energy efficiency for digital circuits over a very wide operating range, starting from small devices with a power budget of less than a mW that will drive Internet of Things (IoT) applications, all the way to High Performance Computing (HPC) systems such as data centers that consume power in the MWs. Limitations in available energy for mobile devices, maximum power density in tightly integrated circuits and the significant costs associated with running and cooling data centers all require solutions where circuits need to be able to do more with available energy than ever before. The research in the group concentrates on improving this efficiency by at least an order of magnitude which will be the key to enable digital solutions of the future.

We improve energy efficiency by embracing parallelization, by making sense of data close to where it is produced thereby reducing the communication overhead, by making the best use of the latest technological developments in integrated circuits and by designing heterogeneous systems where customizable accelerators enhance general purpose processing.

The flagship project of the group is PULP (Parallel Ultra Low Power) processing platform which is a cluster based system, where each cluster consists of small and efficient processors that have access to a common data memory which allows parallel single cycle access as long as there are no contentions. When the workload is favorable, cores are operated at near threshold voltage where the efficiency is the highest, or are completely switched off when they are not needed. We also take advantage of what state of the art manufacturing technologies can provide, such as using extended body biasing techniques enabled by the FDSOI process for example. When used in combination, all these techniques allow us to increase the efficiency of the system far above what was possible before, and we plan to reach and exceed 1 Gops/mW over a large operation range on a programmable architecture in the coming years.

The group covers all aspects of digital system design from technological aspects, circuit and architecture design, demonstrators for various applications, all the way to how these new systems can be programmed. Application fields include, biomedical devices, smart sensors, video processing, telecommunication and high-performance computing.

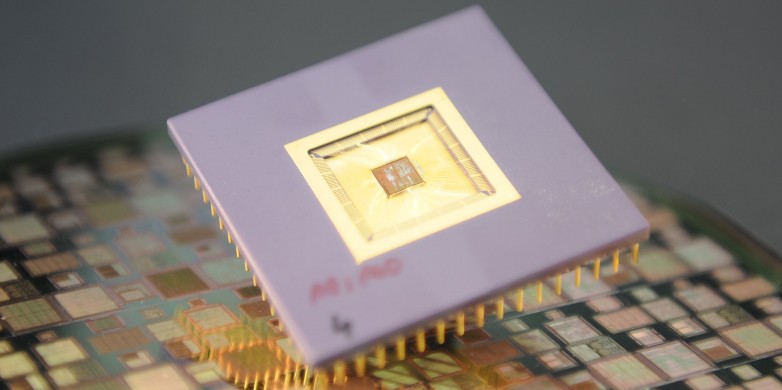

The group has a long tradition of designing integrated circuits, see our chip gallery (http://asic.ethz.ch) that contains information on more than 430 chips that were manufactured over time, with more than 10 chips added to this list every year. We use the latest technologies available to universities in the world (such as the STM 28nm FDSOI since 2014), and through a series of lectures allow all interested students to design and test their own digital circuits in 65nm technology.

Our student projects can be found on the IIS-Projects page.

Administrative Contact

Dig. Integr. Schaltungen u. Syst.

Gloriastrasse 35

8092

Zürich

Switzerland