Integrated Information Processing (IIP)

The research of the Integrated Information Processing (IIP) Group, led by Prof. Christoph Studer , is at the intersection of wireless communication, machine learning, digital signal processing, and very-large-scale integration (VLSI) circuit and system design. The overarching theme is the development of novel algorithms for applications that demand high throughput, low power, and best solution quality, and the integration of corresponding hardware accelerators into efficient (in terms of power consumption, throughput, and silicon area) application-specific integrated circuits (ASICs) and field-programmable gate arrays (FPGAs). To arrive at best-in-class ASIC designs and FPGA prototypes, we jointly consider theory, algorithm development, architecture design, and hardware implementation aspects, which enables far more efficient solutions than conventional, atomistic design approaches that solely focus either on theory, algorithms, or on circuit design.

Our current research activities are in beyond-fifth-generation (B5G) multi-antenna wireless communication systems, simultaneous sensing and communication (SISCO), positioning with wireless signals (including privacy aspects), analog-to-feature (A2F) conversion for low-power signal classification, (non-)convex optimization for digital signal processing, and hardware-efficient machine learning in the realm of wireless systems. In all of these fields, we leverage a wide range of mathematical and algorithmic tools, including convex and non-convex optimization, sparse signal recovery and compressive sensing, graphical models and message passing, Bayesian inference, nonparametric estimation, Monte-Carlo methods, supervised and self-supervised deep learning, dimensionality reduction, and manifold learning. Furthermore, insights gained from our hardware prototypes often inspire new theory and algorithms.

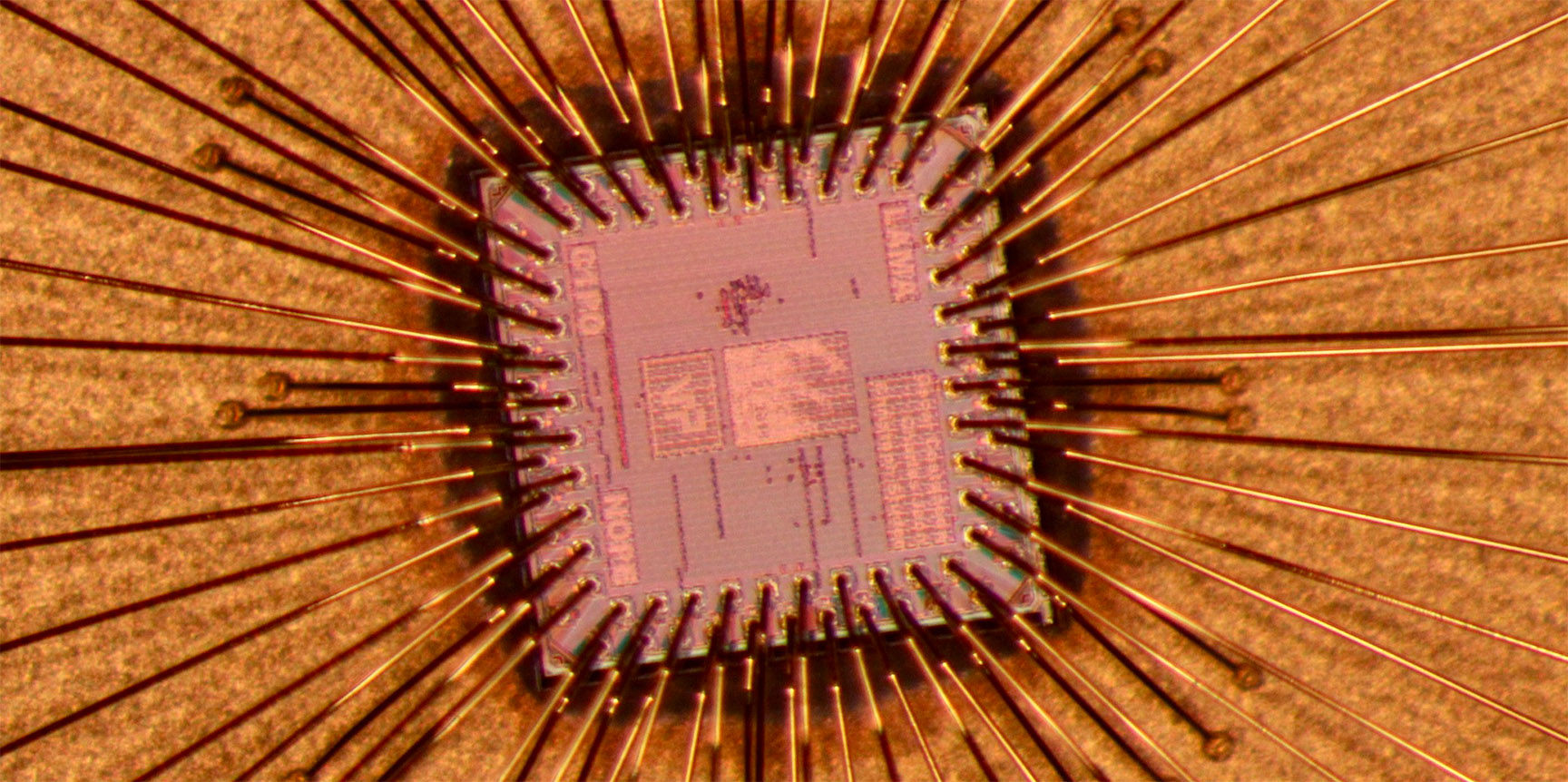

The Integrated Information Processing (IIP) Group has developed a large number of application-specific integrated circuits (ASICs) in CMOS technologies ranging from UMC 250nm to TSMC 28nm, many of them in collaboration with the Microelectronics Design Center .

Furthermore, the IIP Group has expertise in the development of FPGA- and processor-based hardware demonstrators for applications in wireless systems and digital signal processing.

Student Projects

The student projects offered by the IIP Group can be found at the IIS-Projects website.

More information

iip.ethz.chAdministrative Contact

Institut für Integrierte Systeme

Gloriastrasse 35

8092

Zürich

Switzerland